## MICROCONTROLLER

UNIT-III Lecture-3

# Mode 2 Programming

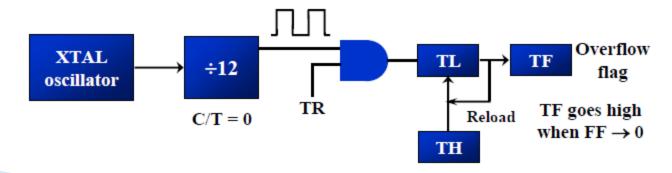

- The following are the characteristics and operations of mode 2:

- (1.) It is an 8-bit timer; therefore, it allows only values of 00 to FFH to be loaded into the timer's register TH

- (2.) After TH is loaded with the 8-bit value, the 8051 gives a copy of it to TL

- Then the timer must be started

- This is done by the instruction SETB TR0 for timer 0 and SETB TR1 for timer 1

- (3.) After the timer is started, it starts to count up by incrementing the TL register

- It counts up until it reaches its limit of FFH

- When it rolls over from FFH to 00, it sets high the TF (timer flag)

- When the TL register rolls from FFH to 0 and TF is set to 1, TL is reloaded automatically with the original value kept by the TH register

- To repeat the process, we must simply clear TF and let it go without any need by the programmer to reload the original value

- This makes mode 2 an auto-reload, in contrast with mode 1 in which the programmer has to reload TH and TL

# C/T Bit in TMOD Register

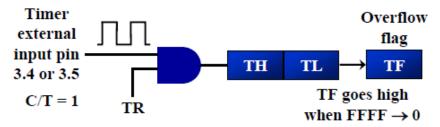

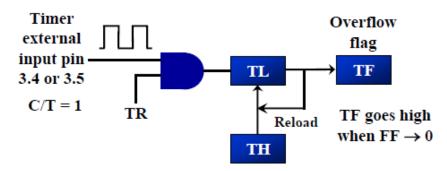

- The C/T bit in the TMOD registers decides the source of the clock for the timer

- When C/T = 1, the timer is used as a counter and gets its pulses from outside the 8051

- The counter counts up as pulses are fed from pins 14 and 15, these pins are called T0 (timer 0 input) and T1 (timer 1 input)

| Pin | Port Pin | Function | Description                    |  |  |

|-----|----------|----------|--------------------------------|--|--|

| 14  | P3.4     | T0       | Timer/counter 0 external input |  |  |

| 15  | P3.5     | T1       | Timer/counter 1 external input |  |  |

#### Timer with external input (Mode 1)

#### Timer with external input (Mode 2)

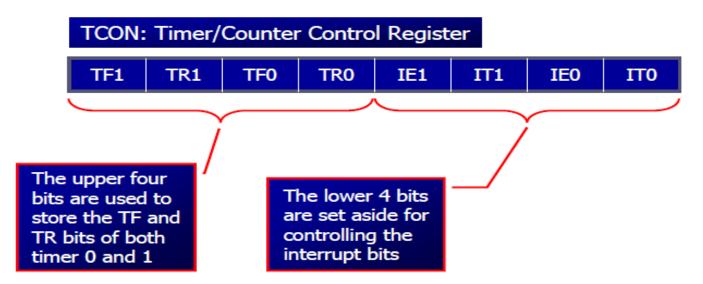

# TCON Register

TCON (timer control) register is an 8bit register

TCON register is a bit-addressable register

#### Equivalent instruction for the Timer Control Register

| For timer 0 |     |   |      |        |  |  |  |

|-------------|-----|---|------|--------|--|--|--|

| SETB        | TR0 | = | SETB | TCON.4 |  |  |  |

| CLR         | TR0 | = | CLR  | TCON.4 |  |  |  |

| SETB        | TF0 | = | SETB | TCON.5 |  |  |  |

| CLR         | TF0 | = | CLR  | TCON.5 |  |  |  |

| For timer 1 |     |   |      |        |  |  |  |

| SETB        | TR1 | = | SETB | TCON.6 |  |  |  |

| CLR         | TR1 | = | CLR  | TCON.6 |  |  |  |

| SETB        | TF1 | = | SETB | TCON.7 |  |  |  |

| CLR         | TF1 | = | CLR  | TCON.7 |  |  |  |